Trion FPGA 製品概要

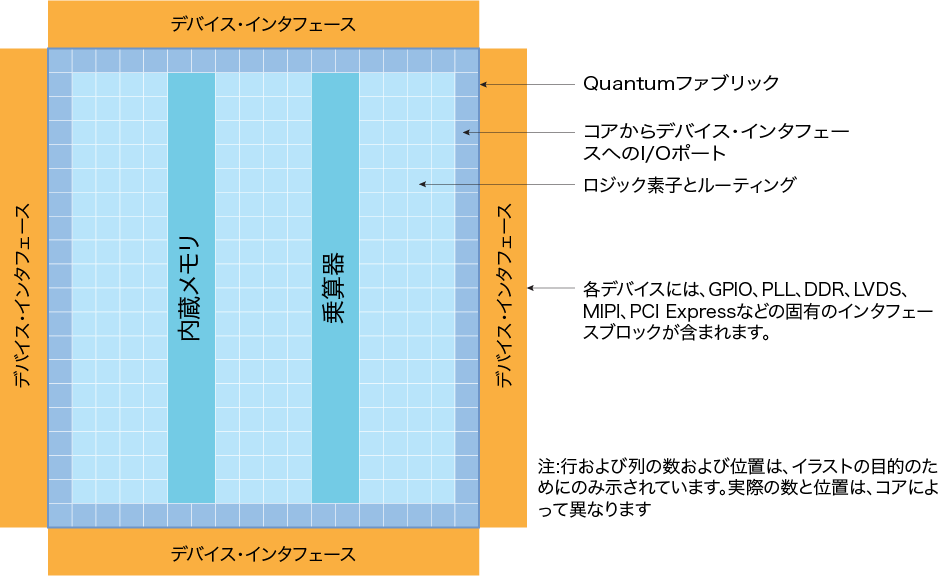

エフィニックス (Efinix®) Trion® プログラマブル・プラットフォームは、当社の Quantum™ テクノロジをベースに構築されており、従来の FPGA 製品と比較して、パワー・パフォーマンス・エリアに大きな優位性をもたらします。Trion FPGA は、プログラマブル・ロジックと Quantum テクノロジを使用したルーティング・ファブリックを特徴としています。このファブリックは、外周に I/O インターフェイスを持ち、モバイルや IoT などの多くの大量生産アプリケーションで必要とされる小型パッケージ要求を満足します。ロジックおよびルーティングに加えて、内蔵メモリと乗算器ブロック (または DSP ブロック) が含まれています。

この Trion プラットフォームは SMIC 40nm LL プロセスで製造され、4,000 ~ 20万ロジック・エレメント (LE) のロジック集積度を持ち、GPIO、PLL、発振器、MIPI、DDR、LVDS などの標準インターフェイスを内蔵しています。Trion FPGA は、汎用カスタム・ロジック市場 (モバイル、IoT、一般的なコンシューマ製品、産業機器、医療機器など) をターゲットにしています。また、エッジデバイスでの深層学習や演算アクセラレーターのような急成長している市場もサポートします。

シンプルで使いやすいソリューション

Trion T4、T8、T13、および T20 FPGA では、49、81 ボールの FineLine BGA のような小型のパッケージが用意されており、迅速な市場投入を必要とする小型、低消費電力アプリケーションに最適です。モバイル、IoT、ウェアラブル、AR/VR 用のコネクティビティ、その他のコンシューマ製品などで使用可能です。

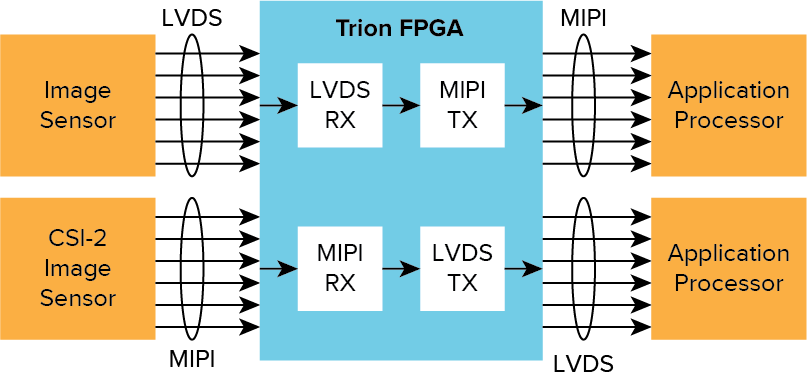

I/O 集約型ソリューション

Trion T13、T20、T55、T85、および T120 FPGA は、GPIO や LVDS ピンを多数備えているため、高帯域幅インターフェイスのブリッジや I/O 拡張に役立ちます。これらの I/O 豊富な FPGA は、放送、ディスプレイ、制御、オートメーション、ロボティクスなどのアプリケーションをサポートします。

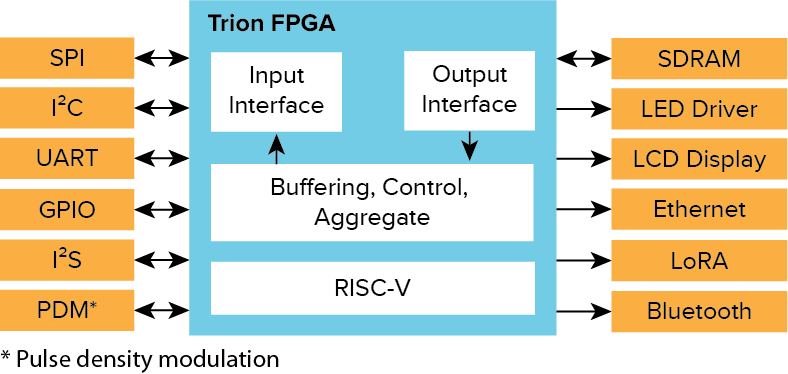

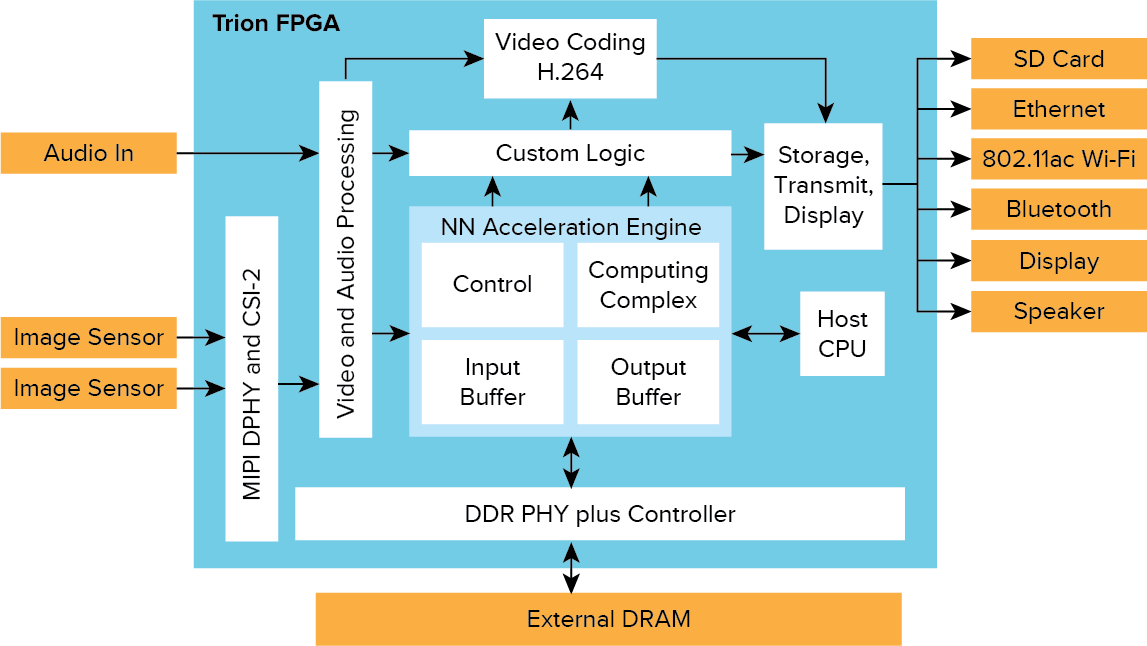

完全なシステムソリューション

DDR3/LPDDR3 メモリ・インターフェイス、MIPI インターフェイス、ソフト・プロセッサ・システム (RISC-V など) を搭載したTrion T13、T20、T35、T55、T85 および T120 FPGAを使用することで、スマートホーム製品、監視カメラ、業務用カメラ、ハイエンド・インテリジェント・システムなどのアプリケーション向けの完全なシステム・ソリューションを構築することができます。

Trion FPGA の中核をなす Quantum コアの微細なアーキテクチャは、演算を要する機械学習アルゴリズムやディープ・ニューラル・ネットワークの構築に最適です。十分なロジック・エレメント、DSP ブロック、オンチップ RAM を搭載した T120 は、INT8 精度の CNN では 1 TOPS、BNN では 5 TOPSを実現します。

Trion FPGA ブロック図

製品ラインナップとパッケージ

ラインナップとインターフェイス

| 機能 | T4 | T8 | T13 | T20 | T35 | T55 | T85 | T120 |

|---|---|---|---|---|---|---|---|---|

| ロジック・エレメント (LE) | 3,888 | 7,384 | 12,828 | 19,728 | 31,680 | 54,195 | 84,096 | 112, 128 |

| マスク・プログラマブル メモリ (MPM) | – | – | – | – | ||||

| 内蔵メモリビット (kb) | 77 | 123 | 727 | 1,044 | 1,475 | 2,765 | 4,055 | 5,407 |

| 18×18 乗算器 | 4 | 8 | 24 | 36 | 120 | 150 | 240 | 320 |

| PLL | 1 | 5 | 5 | 7 | 7 | 8 | 8 | 8 |

| 最大 GPIO 本数 (1) | 55 | 97 | 195 | 222 | 222 | 278 | 278 | 278 |

| LVDS (TX, RX) | – | 6, 6 | 13, 13 | 20, 26 | 20, 26 | 52, 52 | 52, 52 | 52, 52 |

| DDR3, LPDDR3, LPDDR2 (1066 Mbps) | – | – | – | x16 | x16 | x32 | x32 | x32 |

| MIPI DPHY (4レーン) 内蔵 MIPI CSI-2 コントローラ | – | – | 2 RX 2 TX | 2 RX 2 TX | 2 RX 2 TX | 3 RX 3 TX | 3 RX 3 TX | 3 RX 3 TX |

(1) MIPI および DDR インターフェイスは専用の I/O を使用しますので、最大 GPIO 本数は、それらのインターフェイスの I/O 数を含みません。

パッケージ オプション

| 機能 | T4 | T8 | T13 | T20 | T35 | T55 | T85 | T120 |

|---|---|---|---|---|---|---|---|---|

| 49 ボール FBGA (0.4 mm、3×3 mm) | ||||||||

| 80 ボール WLCSP (0.4 mm, 4.5×3.6 mm) | ||||||||

| 81 ボール FBGA (0.5 mm、5×5 mm) | ||||||||

| 144 ピン LQFP (0.5 mm、20×20 mm) | ||||||||

| 169 ボール FBGA (0.65 mm、9×9 mm) | ||||||||

| 256 ボール FBGA (0.8 mm、13×13 mm) | ||||||||

| 324 ボール FBGA (0.65 mm、12×12 mm) | ||||||||

| 400 ボール FBGA (0.8 mm、16×16 mm) | ||||||||

| 484 ボール FBGA (0.8 mm、18×18 mm) | ||||||||

| 576 ボール FBGA (0.65 mm、16×16 mm) |

標準 I/O インターフェイス

現在 Trion FPGA は以下のインターフェイスをサポートします

- MIPI MIPI D-PHY (4レーン) 最大6 Gbps およびハード IP として実装された CSI-2 コントローラにより、低電力、低コストを実現し、ロイヤルティフリーで容易に実装可能です。

- LVDS 最大 LVDS データレート 800 Mbps、トータル 41.6 Gbps の帯域幅をサポートします。

- DDR 最大 DDRラインレート 1066 Mbps、トータル 51.2 Gbps のピーク帯域幅で、DDR3、LPDDR3、および LPDDR2 をサポートします。DDR インターフェイスは、ハード IP の PHY およびコントローラにより、低電力、低コストを実現し、容易に組み込むことが可能です。

マスク・プログラマブル・メモリ (MPM)

T4、T8、T13、および T20 FPGA には、MPM というオプションが装備されています。この機能は、外部シリアル・フラッシュデバイスによる FPGA のコンフィギュレーションの代わりにオンチップ MPM を使用するものです。このオプションは、超小型化の必要性のあるシステムや低コストが求められるシステムなどでの大量生産時に外部シリアル・フラッシュデバイスを削減するためのものです。MPMは、工場出荷時に実施する 1 回限りのプログラムオプションのため、NRE (開発費) がかかります。MPMを使用するためには、コンフィギュレーションデータを当社に提供いただき、当社のアプリケーション・エンジニアが専用のデータマスクに変換し、MPM データとして組み込みます。

Efinity ソフトウェア サポート

Efinity® ソフトウェアは、RTL デザインからビットストリーム生成 (論理合成、配置配線、タイミング解析を含む) までの完全なツールフローを提供します。ソフトウェアには、プロジェクトの設定、ツールフローの実行、および結果の表示を視覚的に操作するための GUI (グラフィカル・ユーザ・インターフェイス) およびコマンドライン・フロー、Tcl コマンド・コンソールが用意されています。ソフトウェアで生成されたビットストリーム・ファイルにより Trion FPGA をコンフィギュレーションします。ソフトウェアは、Verilog HDL 言語と VHDL 言語をサポートしています。

リソース

Trion FPGA について

※データシートは最新ではない場合がございます。